## **Description**

WF306TBM is one ASK transmitter for remote control application. The circuit working frequency range is about 300MHz-450MHz. It is mainly intended for the ISM (Industrial, Scientific and Medical) band 315/433MHz.

WF306TBM integrates one phase-locked loop (PLL) and MCU to set different working frequency and select the transmitting power.

WF306TBM is designed for remote wireless control systems. It is available in SOP-16 package and working over the extended temperature range (-40 to +85°C).

#### **Features**

- Working frequency range: 300MHz-450MHz.

- Tunable output power: 13dBm @ 3V with 50 ohm load, typ.

- Low supply voltage: 2.3V-3.6V for 315/433MHz.

- Low supply voltage detection

- Automatic shutdown protection

- 3-wire SPI interface.

# **Applications**

- Remote Keyless Entry (RKE)

- · Remote Control, Garage door and gate openers

- AMR-Automatic Meter Reading

- Wireless alarm and security system.

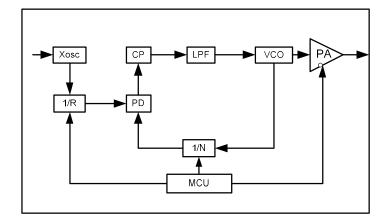

### **Block Diagram**

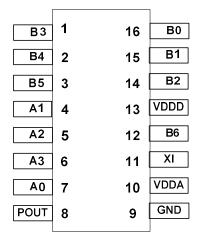

# **Pin Configuration**

**Table 1. Pin Description**

| Pin | Symbol | I/O | Description                                                                                                                                                                                                                                                   |  |  |  |

|-----|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | В3     | I   | Input pin or open-drain output pin with system wake-up function System clear (RESET) input. Active low RESET to the device. Weak pull-high always on if configured as RSTB. Voltage on this pin must not exceed VDD, See IOB3 diagram for detail description. |  |  |  |

| 2   | В4     | I/O | Bi-direction I/O pin with system wake-up function (RCOUT optional in IRC/ERIC, ERC mode) Software controlled pull-high/open-drain Oscillator crystal output (HF, XT, LF mode) Outputs with the instruction cycle rate (RCOUT optional in IRC/ERIC, ERC mode)  |  |  |  |

| 3   | B5     | I/O | Bi-direction I/O pin with system wake-up function(IRC mode) Software controlled pull-high/open-drain Oscillator crystal input(HF,XT,LF mode) External clock source input(ERIC,ERC mode)                                                                       |  |  |  |

| 4   | A1     | I/O | A0 ~ A3 as bi-direction I/O pin Software controlled pull-down                                                                                                                                                                                                 |  |  |  |

| 5   | A2     | I/O | A0 ~ A3 as bi-direction I/O pin Software controlled pull-down                                                                                                                                                                                                 |  |  |  |

| 6   | A3     | I/O | A0 ~ A3 as bi-direction I/O pin Software controlled pull-down                                                                                                                                                                                                 |  |  |  |

| 7   | A0     | I/O | A0 ~ A3 as bi-direction I/O pin Software controlled pull-down                                                                                                                                                                                                 |  |  |  |

| 8   | POUT   |     | Transmitted RF output                                                                                                                                                                                                                                         |  |  |  |

| 9   | GND    |     | Ground                                                                                                                                                                                                                                                        |  |  |  |

| 10  | VDDA   |     | Analog circuit Power suplly                                                                                                                                                                                                                                   |  |  |  |

| 11  | XI     |     | Input terminal of local oscillation signal.It is connected to the crystal or driven by an external clock.                                                                                                                                                     |  |  |  |

| 12  | В6     | I/O | Bi-direction I/O pin with system wake-up function Software controlled pull-high/open-drain                                                                                                                                                                    |  |  |  |

| 13 | VDDD |     | Digital circuit Power supply                                                                                                              |

|----|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

| 14 | B2   | I/O | Bi-direction I/O pin with system wake-up function<br>Software controlled pull-high/open-drain/pull-down<br>External clock input to Timer0 |

| 15 | B1   | I/O | Bi-direction I/O pin with system wake-up function Software controlled pull-high/open-drain/pull-down                                      |

| 16 | В0   | I/O | Bi-direction I/O pin with system wake-up function Software controlled pull-high/open-drain/pull-down External interrupt input             |

Note: A0 connect to WF306TBM SDIN, B6 connect to WF306TBM SEN, B7 connect to WF306TBM SCLK

**Table 2. Absolute Maximum Rating**

| Item                     | Rating           |

|--------------------------|------------------|

| Supply Voltage, VDD      | + 5.6V           |

| Inputs and Clock Outputs | - 0.5V to + 5.6V |

| Storage Temperature      | - 65 to + 150 oC |

| Soldering Temperature    | + 260 oC         |

**Table 3. Electrical Specifications**

| Parameter                      | Symbol           | Test Condition         | Min | Тур | Max | Unit |

|--------------------------------|------------------|------------------------|-----|-----|-----|------|

| Supply<br>Voltage              | V <sub>DD</sub>  | 300MHz-450MHz          | 2.3 | 3.0 | 3.6 | V    |

| Supply<br>Current              | I <sub>DD</sub>  | Fout=434MHz, 13dBm, 3V |     | 13  |     | mA   |

| RF Power<br>On/Off Ratio       | Pratio           | 300MHz-450MHz          |     | 60  |     | dB   |

| Pout supply voltage            | Pvol             | 300MHz-450MHz          |     |     | 3.6 | V    |

| Transmitted                    | Pout             | Fin=315MHz, Vdd=5V     |     | 10  |     | dBm  |

| Power                          | Tout             | Fin=434MHz, Vdd=5V     |     | 10  |     | dBm  |

| Data Rate                      |                  | OOK/ASK mode           | 0.5 |     | 10  | Kb/s |

| OSCI<br>operating<br>Frequency | F <sub>osc</sub> |                        | 9   | 10  | 20  | MHz  |

| RC-OSC                         | Rosc             | RC Oscillator          |     | 4   |     | MHz  |

| Operating<br>Temperature       | T <sub>a</sub>   |                        | -40 | 27  | 85  | °C   |

| Leakage<br>Current             | I                | Power down mode        |     |     | 1   | uA   |

|                                |                  |                        |     |     |     |      |

# **Functional Description**

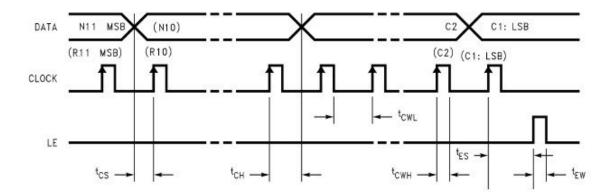

#### **Serial Data input and Timing**

WF306TBM has 3-wire interfaceCLK, DATA, LE) to set R counter, PLL N counter, and other parameters. At the rising edge of CLK, DATA are written into shift-register (MSB: first input data; LSB: last input data). At the rising edge of LE, stored data is loaded into mid-latches.

Note: (1) MSB loaded first.

(

(2) WhenWF 306TBM power is disconnected CLK,DATA, LE are pulled at low

| Symbol           | Parameter                  | Min                                                                                                                                                 | Max                                                                                                                                                                                                                                                                                          | Unit                                                                                                                                                                     |

|------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>CS</sub>  | Data to Clock Setup time   | 10. 5                                                                                                                                               |                                                                                                                                                                                                                                                                                              | μs                                                                                                                                                                       |

| t <sub>CH</sub>  | Data to Clock Hold time    | 22                                                                                                                                                  |                                                                                                                                                                                                                                                                                              | μs                                                                                                                                                                       |

| t <sub>CWH</sub> | Clock Pulse width High     | 10. 5                                                                                                                                               |                                                                                                                                                                                                                                                                                              | μs                                                                                                                                                                       |

| t CWL            | Clock Pulse width Low      | 20. 5                                                                                                                                               |                                                                                                                                                                                                                                                                                              | μs                                                                                                                                                                       |

| t <sub>ES</sub>  | Clock to LE Setup time     | 10                                                                                                                                                  |                                                                                                                                                                                                                                                                                              | μs                                                                                                                                                                       |

| t <sub>EW</sub>  | LE pulse width             | 10                                                                                                                                                  |                                                                                                                                                                                                                                                                                              | μs                                                                                                                                                                       |

|                  | t CS t CH t CWH t CWL t ES | t CS Data to Clock Setup time  t CH Data to Clock Hold time  t CWH Clock Pulse width High  t CWL Clock Pulse width Low  t ES Clock to LE Setup time | t CS         Data to Clock Setup time         10.5           t CH         Data to Clock Hold time         22           t CWH         Clock Pulse width High         10.5           t CWL         Clock Pulse width Low         20.5           t ES         Clock to LE Setup time         10 | t CS Data to Clock Setup time 10.5  t CH Data to Clock Hold time 22  t CWH Clock Pulse width High 10.5  t CWL Clock Pulse width Low 20.5  t ES Clock to LE Setup time 10 |

11-Bit data are transfer from shift-register into the latches, MSB first, LSB last. The last two LSB bits control the register address. The bit format is as below.

Where C1, C2 are control bits, determines the register address.

| Register Address control bits | S  | Register | Note |

|-------------------------------|----|----------|------|

| C2                            | C1 |          |      |

| 0                             | 0  | R0       |      |

| 0 | 1 | R1 |  |

|---|---|----|--|

| 1 | 0 | R2 |  |

| 1 | 1 | R3 |  |

For R0 register, R0<8:7> control charge pump current, R0<9> not used.

|     |    | R         | coun | ter |   |   |   | CP cur | rent | Not used |  |  |  |  |

|-----|----|-----------|------|-----|---|---|---|--------|------|----------|--|--|--|--|

| LSB |    |           |      |     |   |   |   |        |      | MSB      |  |  |  |  |

| C1  | C2 | N N N N N |      | N   | N | N |   |        |      |          |  |  |  |  |

|     |    | 1         | 2    | 3   | 4 | 5 | 6 | 7 8 9  |      | 9        |  |  |  |  |

| 0   | 0  |           | RO   |     |   |   |   |        |      |          |  |  |  |  |

| function | R0<8:7 | >   |          |  |

|----------|--------|-----|----------|--|

|          | N8     | N7  | Icp (uA) |  |

|          | 0      | 0 0 |          |  |

|          | 0      | 1   | 1.0      |  |

|          | 1      | 0   | 1.5      |  |

|          | 1      | 1   | 2.0      |  |

R counter is controlled by initial 6-Bits N<6:1>, see below table. Default state, R=10

| R<6:1> | N6 | N5 | N4 | N3 | N2 | N1 |

|--------|----|----|----|----|----|----|

| 1      | 0  | 0  | 0  | 0  | 0  | 0  |

| 1      | 0  | 0  | 0  | 0  | 0  | 1  |

| 2      | 0  | 0  | 0  | 0  | 1  | 0  |

| 3      | 0  | 0  | 0  | 0  | 1  | 1  |

|        |    |    |    |    |    |    |

| 63     | 1  | 1  | 1  | 1  | 1  | 1  |

Note:

- (1) MSB load first.

- (2) R≥1

- (3)  $R = R1x2^0 + R2x2^1 + ... + R6x2^5$ , R = 1 to 64.

For R1 register, R1<9>=1, power down chip. Other bits control B counter.

|     |    | В         | coun | ter |   | Global Powerdown |   |   |   |   |  |  |  |  |  |

|-----|----|-----------|------|-----|---|------------------|---|---|---|---|--|--|--|--|--|

| LSB |    |           |      |     |   | MSB              |   |   |   |   |  |  |  |  |  |

| C1  | C2 | N N N N N |      |     |   | N                | N | N | N | N |  |  |  |  |  |

|     |    | 1         | 2    | 3   | 4 | 5                | 9 |   |   |   |  |  |  |  |  |

| 1   | 0  |           | R1   |     |   |                  |   |   |   |   |  |  |  |  |  |

B counter are controlled through 8-Bits, according to below table, N8 default state is 1, else bits are zeros.

| В   | N8 | N7 | N6 | N5 | N4 | N3 | N2 | N1 |

|-----|----|----|----|----|----|----|----|----|

| 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 1   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

|     |    |    |    |    |    |    |    |    |

| 255 | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

$B = N1x2^{0} + N2x2^{1} + ... + N8x2^{7}, B \ge 1$ , Divider ration: 1 to 255 (B \ge A),

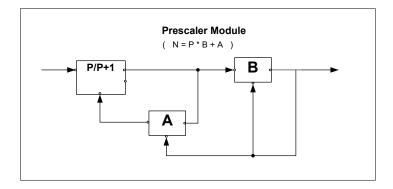

For R2 register, R2<9> not used. R2<8> select N-divider modulus P.

| Mode | Clk | A Counter |   |   |   |   |   | N divider | Spur<br>control |     |

|------|-----|-----------|---|---|---|---|---|-----------|-----------------|-----|

| sel  | sel |           |   |   |   |   |   | select    | control         |     |

| LSB  |     |           |   |   |   |   |   |           |                 | MSB |

| C1   | C2  | N         | N | N | N | N | N | N         | N               | N   |

|      |     | 1         | 2 | 3 | 4 | 5 | 6 | 7         | 8               | 9   |

| 1    | 1   | R2        |   |   |   |   |   |           |                 |     |

|          | R2<8> control N-divider mode |      |  |  |  |  |

|----------|------------------------------|------|--|--|--|--|

|          | 0                            | 1    |  |  |  |  |

| function | P=16                         | P=32 |  |  |  |  |

Counter (N) consists of one 7-Bits SWALLOW COUNTER (A Counter), one 8-Bits PULSE COUNTER (B counter), and one P/(P+1) prescaler. When counter A counts, dual module prescaler divider ration is P+1. When A counter is overflow but B counter still counts, dual module prescaler divider ration is P, P=16, or P=16

$$N = P \times B + A, B \ge A$$

The default state N=320, P=32, B=10, A=0.

A counter is controlled by initial 7-Bits, see below table.

| A   | N7 | N6 | N5 | N4 | N3 | N2 | N1 |

|-----|----|----|----|----|----|----|----|

| 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 1   | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

|     |    |    |    |    |    |    |    |

| 127 | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

Pulse swallow formula: fvco = [(P \* B) + A] \* fosc / R,

- fvco, VCO oscillation frequency

- B, 11-Bits B counter's divider ration, 1-255

- A, swallow A counter's divider ration,  $0 \le A \le 127$ ,  $A \le B$ .

- fosc, crystal oscillation frequency

- R, 6-Bits R counter divider ration, 1-63

- P, dual module prescaler, P = 16/32.

For R3 register, R3<2:1>=1, not used. R3<6:3> control power amplifier transmitting power. R3<9:7>=1, not used.

|     |    | Not used |        | TX power control |        |        |        | Not used |        |        |

|-----|----|----------|--------|------------------|--------|--------|--------|----------|--------|--------|

| LSB |    |          |        |                  |        |        |        |          |        | MSB    |

| C1  | C2 | N<br>1   | N<br>2 | N<br>3           | N<br>4 | N<br>5 | N<br>6 | N<br>7   | N<br>8 | N<br>9 |

| 1   | 1  | R3       |        |                  |        |        |        |          |        |        |

| R3<6:3> | Function, tune TX power |  |

|---------|-------------------------|--|

| 0000    | Def power               |  |

| 0001    | Max power               |  |

| 1110    | Min Power               |  |

#### **Crystal Oscillator**

The crystal oscillator circuit consists of a colpitts oscillator. It can drive 10MHz-30MHz crystal without external capacitors required. The crystal driver stage can also take input clock as input clock buffer.

The R counter is used to divide the crystal clock down to the low frequency clock, which is sent to PFD in PLL block as reference clock.

#### **PLL Block**

The PLL consists of phase-frequency detector (PFD), charge pump, loop filter, voltage-controlled oscillator (VCO), and divider (N). The PFD compares two signals and produces an error signal which is proportional to the two signal phase difference. The error signal is used to control the VCO to run fast or slow.

The divider N counter is selectable through SPI interface. The VCO oscillation frequency range is tunable between 300 MHz-500 MHz.

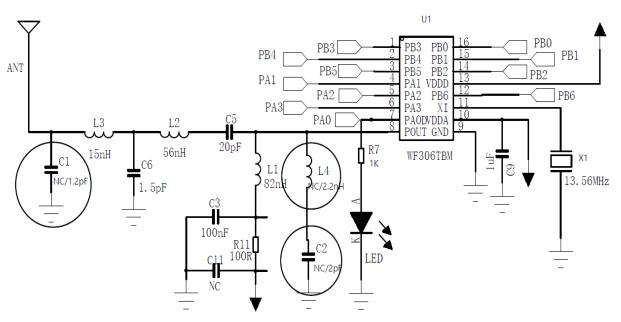

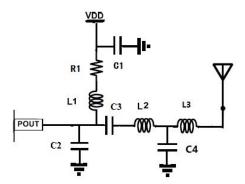

#### **RF OUTPUT**

The POUT pin can be matched to 50 Ohm with a T-type circuit. The supply voltage can be as high as 3.6V. Below table is suggested inductor and capacitor value for different frequency.

| Frequency (MHz) | L1 (nH) | L2<br>(nH) | L3<br>(nH) | C1<br>(uF) | C2<br>(pF) | C3<br>(pF) | C4<br>(pF) | R1<br>(Ω) | Note |

|-----------------|---------|------------|------------|------------|------------|------------|------------|-----------|------|

| 315             | 100     | 82         | 82         | 1.0        | 1.0        | 5          | 1.8        | 100       |      |

| 433             | 82      | 68         | 68         | 1.0        | 1.0        | 5          | 1.2        | 100       |      |

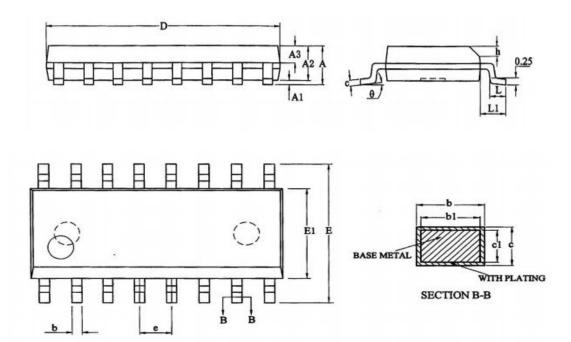

# Package Information SOP-16

| SYMBOL | MILLIMETER |      |                               |  |  |  |  |

|--------|------------|------|-------------------------------|--|--|--|--|

| SYMBOL | MIN        | NOM  | MAX                           |  |  |  |  |

| A      | _          | _    | 1.75                          |  |  |  |  |

| A1     | 0.05       | _    | 0.225                         |  |  |  |  |

| A2     | 1.30       | 1.40 | 1.50                          |  |  |  |  |

| A3     | 0.60       | 0.65 | 0.70                          |  |  |  |  |

| ь      | 0.39       | _    | 0.48                          |  |  |  |  |

| ы      | 0.38       | 0.41 | 0.43<br>0.26<br>0.21<br>10.10 |  |  |  |  |

| С      | 0.21       | _    |                               |  |  |  |  |

| cl     | 0.19       | 0.20 |                               |  |  |  |  |

| D      | 9.70       | 9.90 |                               |  |  |  |  |

| E      | 5.80       | 6.00 | 6.20                          |  |  |  |  |

| EI     | 3.70       | 3.90 | 4.10                          |  |  |  |  |

| e      | 1.27BSC    |      |                               |  |  |  |  |

| h      | 0.25       | _    | 0.50                          |  |  |  |  |

| L      | 0.50       | -    |                               |  |  |  |  |

| Li     | 1.05BSC    |      |                               |  |  |  |  |

| •      | 0          | -    | 8,                            |  |  |  |  |